小尺寸,低功耗,低成本的高性能產品, 為記憶體的RDL加工帶來了強大的市場需求,藉由重新佈線I / O位置,MCP(多芯片封裝)和SiP(系統級封裝)的整合將得以被實現。

Raytek 提供

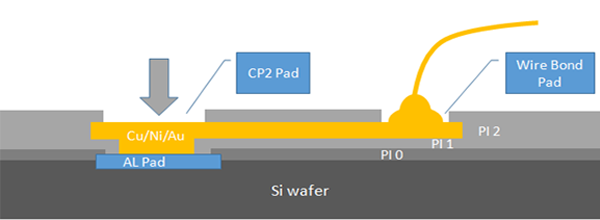

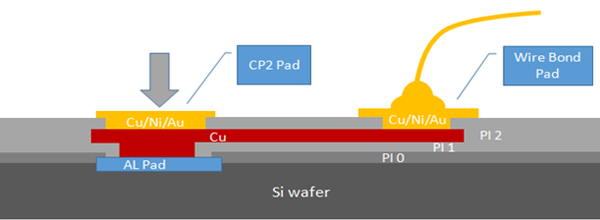

- 相較於重新設計製作記憶體芯片所需非常高的成本和非常長交期, Cu / Ni / Au RDL提供了彈性大的KGD打線位置調整, 完全可滿足不同終端客戶所需的SIP封裝需求,且該KGD RDL芯片在打線過程中,不管是與Au線或Cu線皆可相容。

- Polyimide 200℃低溫固化特性, 避免記憶體芯片電性延遲性受損。

- 多層的Cu RDL設計,在高性能物件的應用上 ,具有共用電源/接地線連接的電性強化作用。

- 銅RDL與銅柱凸塊或無鉛凸塊結合,提供晶圓級CSP應用。

- 5/5 um 細線路有助於封裝的微小化。

| Products | Cu RDL | CuNiAu RDL | Cu RDL+Cu PAD |

Cu RDL+CuNiAu PAD |

|---|---|---|---|---|

| PI1 | 5 um | 5 um | 5 um | 5 um |

| PVD1 Ti/Cu | 0.1/0.2 um | 0.1/0.2 um | 0.1/0.2 um | 0.1/0.2 um |

| ECD1 Cu | 3 ~ 7 um | 3 um | 3 um | 3 um |

| ECD1 Ni | - | 2 um | - | - |

| ECD1 Au | - | 0.3~0.5 um | - | - |

| PI2 | 5 um | 5 um | 5 um | 5 um |

| PVD2 Ti/Cu | - | - | 0.1/0.2 um | 0.1/0.2 um |

| ECD2 Cu | - | - | 7 um | 3 um |

| ECD1 Ni | - | 2 | 2 um | |

| ECD1 Au | - | - | - | 0.3~0.5 um |

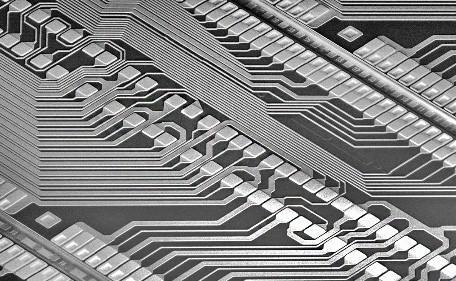

1RDL Fine Line solution (5/5)

8 um/8 um STD RDL

5 um/5 um Fine Pitch

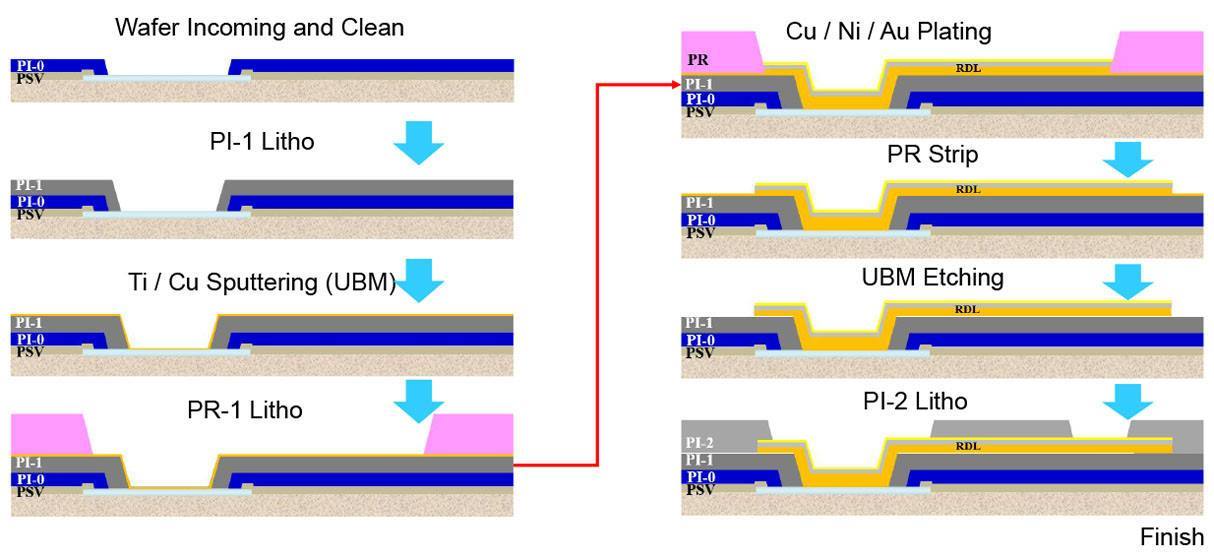

Process Flow of RDL (2P1M)

晶圓線路重佈

晶圓線路重佈