Small form factor , lower power consumption, and high performance product with low cost creates strong market demand for RDL in memory, which can re-route I/O and make integration of MCP (Multi-Chip-Package) and SiP (System in Package) achievable.

Raytek offers

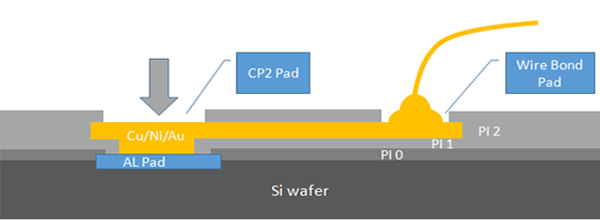

- Cu/Ni/Au RDL to support Memory makers in flexible pad layout KGD to meet variant end users in SiP design comparing very high cost and long cycle time in re-tape out the Memory chip. This KGD chip is compatible with Au and Cu wire bond in assembly process.

- Polyimide curing at 200 degree C prevents Memory suffering data retention rate.

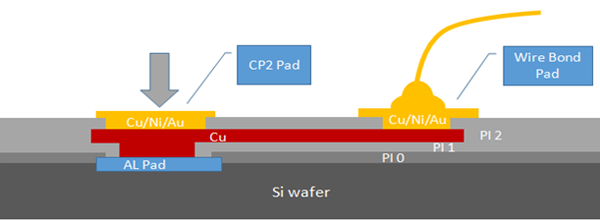

- Cu RDL applied to multilayer RDL, and electrical enhancement with common power/common ground trace connection for high performance device.

- Cu RDL combines with copper pillar bump or lead free bump to serve Wafer level CSP application.

- 5/5 um fine pitch RDL is good for package form factor.

| Products | Cu RDL | CuNiAu RDL | Cu RDL+Cu PAD |

Cu RDL+CuNiAu PAD |

|---|---|---|---|---|

| PI1 | 5 um | 5 um | 5 um | 5 um |

| PVD1 Ti/Cu | 0.1/0.2 um | 0.1/0.2 um | 0.1/0.2 um | 0.1/0.2 um |

| ECD1 Cu | 3 ~ 7 um | 3 um | 3 um | 3 um |

| ECD1 Ni | - | 2 um | - | - |

| ECD1 Au | - | 0.3~0.5 um | - | - |

| PI2 | 5 um | 5 um | 5 um | 5 um |

| PVD2 Ti/Cu | - | - | 0.1/0.2 um | 0.1/0.2 um |

| ECD2 Cu | - | - | 7 um | 3 um |

| ECD1 Ni | - | 2 | 2 um | |

| ECD1 Au | - | - | - | 0.3~0.5 um |

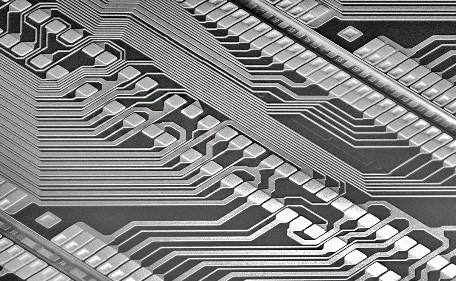

1RDL Fine Line solution (5/5)

8 um/8 um STD RDL

5 um/5 um Fine Pitch

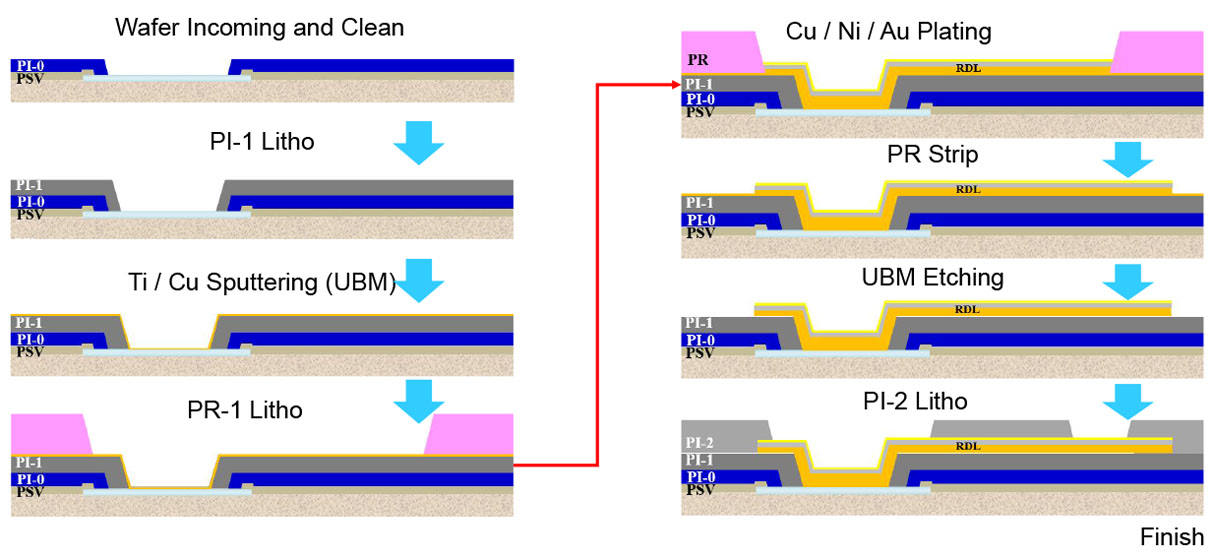

Process Flow of RDL (2P1M)