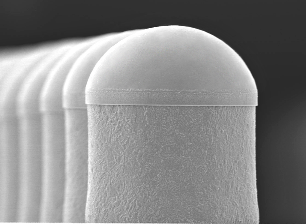

銅柱凸塊的精細凸塊間距可以達到小至50微米,因此提高了Flipchip在載板及模組的封裝能力。而無鉛凸塊(SnAg1.8%)則可以滿足RoHS和綠色產品要求。

Raytek 提供

- 微小到40 um間距,25 um凸塊尺寸銅柱凸塊是可用的,高達150 um間距也是可行的。

- 銅柱凸塊高度可高達75 um, 樣品打樣可達135 um。

- Polyimide 200℃低溫固化特性,避免記憶體芯片電性延遲性受損。

- 提供高溫375℃ polyimide,可用於邏輯芯片。

- 銅柱凸塊結構可提供Cu / SnAg和Cu / Ni / SnAg 兩者成分。

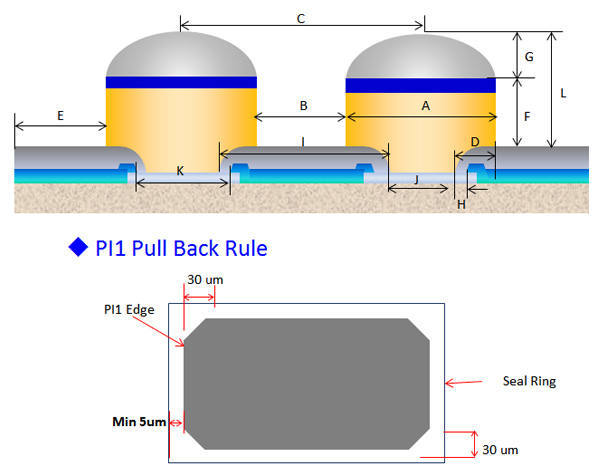

- 提供Polyimide pull in 及 pull out兩種設計,擴大Al墊開口設計的靈活性。

| Products | Cu Pillar | Cu Pillar Bump | Lead Free Bump | Cu RDL + LFB |

|---|---|---|---|---|

| PI | 5 um | 5 um | 5 um | 5 um |

| PVD1 Ti/Cu | 0.1/0.2 um | 0.1/0.2 um | 0.1/0.5 um | RDL 0.1/0.2 um UBM 0.1/0.5 um |

| ECD Cu | 65 ~ 2 um | 35 ~ 7 um | - | 3 um RDL |

| ECD Ni | - | 3 um | 3 um | 3 um |

| ECD SnAg(1.8%) | - | 35 ~15 um | ≦100 um | ≦100 um |

| Symbol | Description | Design Rule |

|---|---|---|

| A | Bump size (PI1:HD4104) | Min. 35 um |

| Bump size (PI1:BM300) | Min. 45 um | |

| B | Bump space | Min. 15 um |

| C | Bump pitch (PI1:HD4104) | Min. 50 um |

| Bump pitch (PI1:BM300) | Min. 60 um | |

| D | Bump edge to PI1 opening | Min. 7.5um |

| E | Bump edge to die edge | Min. 50 um |

| F | Cu post height | ≦ Bump Size |

| G | Solder cap height | ≦1/2 Bump Size |

| H | PI1 to PSV overlap | Min. 5 um |

| I | PI1 width | Min. 35 um |

| J | PI1 opening (PI1:HD4104) | Min. 20 um |

| PI1 opening (PI1:BM300) | Min. 30 um | |

| K | PSV opening (PI1:HD4104) | Min. 30 um |

| PSV opening (PI1:BM300) | Min. 40 um | |

| L | Bump height (before reflow) | Max. 60 um |

| Bump height (after reflow) | Max. 75 um | |

| Fuse exposure | Not allow | |

| Bump plating ratio | 1.47~88.38 % (Machine Limit) |

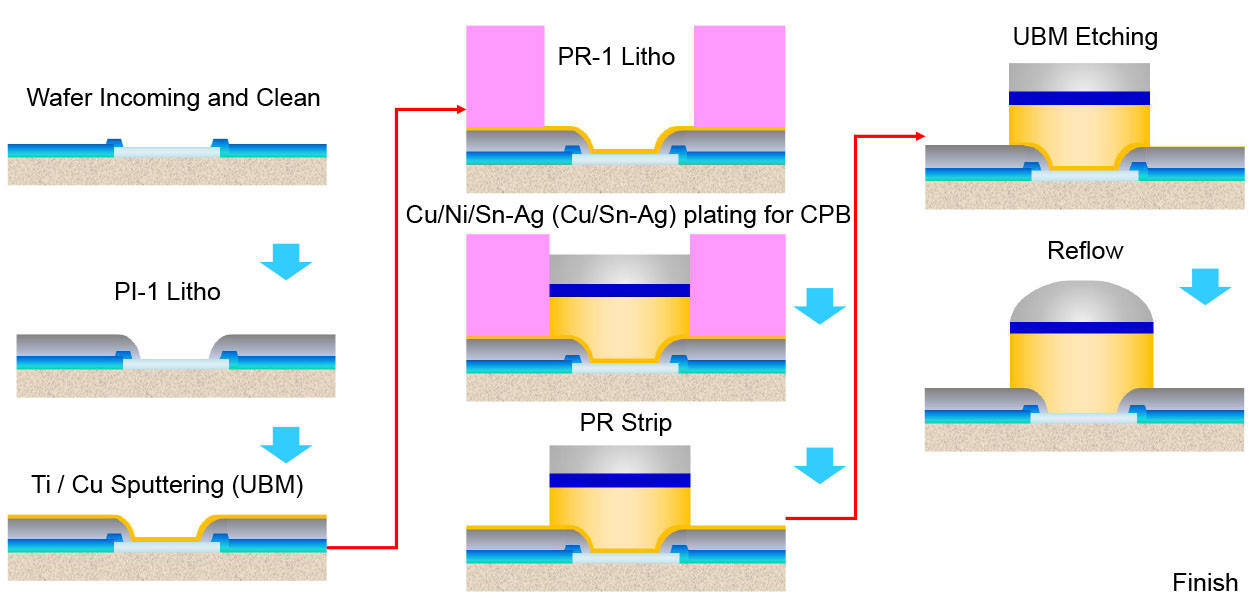

Cu pillar Bump Process Flow

銅柱凸塊

銅柱凸塊